مارک لیو: لیتوگرافی سه نانومتری TSMC مطابق برنامه پیش میرود

مارک لیو، رئیس هیئتمدیرهی شرکت صنایع نیمه هادی تایوان (TSMC)، بهتازگی رسما تأیید کرده است نسل بعد لیتوگرافی این شرکت یعنی لیتوگرافی سه نانومتری، طبق برنامهی تعیینشده پیش میرود. براساس گزارش Wccftech، شرکت TSMC که مشتریان بسیار زیادی دارد و برای تعداد زیادی از شرکتها در سراسر دنیا تراشه تولید میکند، اخیرا از احداث کارخانهای به منظور ساخت تراشهی سه نانومتری در آیندهی نزدیک خبر داده است. این شرکت تایوانی امیدوار است در سال آیندهی میلادی تولید تراشهی مبتنی بر لیتوگرافی سه نانومتری را آغاز کند.

براساس نظرات مارک لیو با محوریت فناوری تولیدی بعدی TSMC، این شرکت اعتقاد دارد که با پیشبرد فعالیتهایش میتواند تقاضا برای تراشههای فعلی و تراشههای آیندهی خود را به شکل مناسب و همزمان پاسخ بدهد. TSMC با برنامهریزی مناسب قصد دارد در مسیری پیش برود که نگذارد تقاضای افزایشیافته برای تراشهی صنعت خودرو روی خروجی دیگر تراشههای این شرکت اثر بگذارد. سخنان مارک لیو در جریان برگزاری کنفرانس بینالمللی مدارهای حالت جامد (ISSCC) با عنوان «رونمایی آیندهی نوآوری» مطرح شدند.

شماری از رسانههای حوزهی سختافزار به اشتباه از سخنان دکتر مارک لیو اینگونه برداشت کردند که فرایند توسعهی لیتوگرافی سه نانومتری TSMC جلوتر از برنامه است. کنفرانس ۲۷ دقیقهای لیو بهصراحت به چنین جملهای اشاره نکرد و در بخش آغازین و پایانی سخنان او شاهد اشاره به مبحث لیتوگرافی سه نانومتری بودیم. دکتر لیو گفت: «به هر حال توسعهی فناوری سه نانومتری پیشرفت خوبی تجربه میکند و بهخوبی مطابق برنامهی ما است.» او همچنین جدیدترین آمار لیتوگرافی سه نانومتری را ارائه داد و تفکراتش دربارهی وضعیت فعلی توسعهی فرآیندهای پردازشی را به زبان آورد.

به گفتهی مارک لیو، تا به امروز TSMC موفق شده است تقریبا ۱٫۸ میلیارد تراشه بر پایهی لیتوگرافی هفت نانومتری بسازد. تا سال گذشتهی میلادی، پیشرفتهترین لیتوگرافی TSMC، نسخهی هفت نانومتری بود؛ اما امروزه این شرکت توانسته است لیتوگرافی پنج نانومتری را نیز به تولید انبوه برساند و به مرور زمان آن را به اصلیترین لیتوگرافی خود تبدیل میکند.

براساس ادعای رئیس هیئتمدیرهی TSMC، لیتوگرافی EUV به شرکت تایوانی امکان داده است بتواند به وفاداری الگویی (Patterning Fidelity) بیشتر و چرخهی تولید کوتاهتر دست یابد و پیچیدگی فرآیندهای تولیدی و نرخ خرابی را کاهش بدهد. مارک لیو میگوید TSMC از فناوری EUV روی ۱۰ لایهی پوششی برای لیتوگرافی پنج نانومتری استفاده میکند. بهطور مشخصتر، EUV در برش خطی و الگوسازی خطی تماسی و فلزی مورد استفاده قرار میگیرد و در این مواقع یک لایهی EUV جایگزین چندین لایهی مربوط به فناوریهای پیشین میشود که از لیتوگرافی DUV استفاده میکردند.

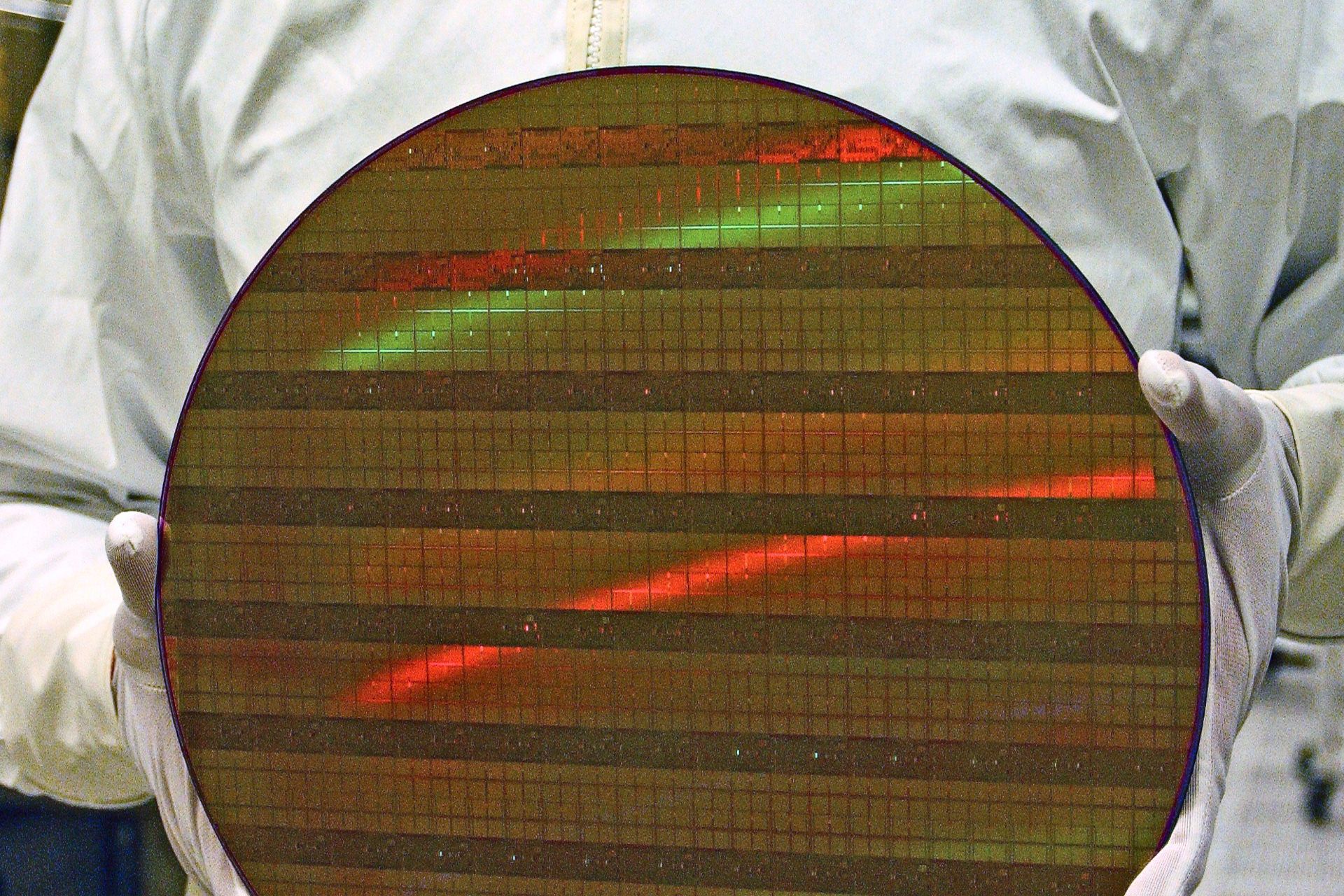

مارک لیو در ادامهی سخنان خود گفت چگونه مبحث بهینهسازی متقابل فناوریهای طراحی (DTCO) طی سالهای گذشته برای تولید تراشه اهمیت بسیار بیشتری پیدا کرده است. DTCO به تراشهسازان امکان میدهد از طراحی و فناوریهای تولیدی به پیشنیازهای تعیینشده در زمینهی عملکرد پردازشی پایبند بمانند. آنطور که رئیس هیئتمدیرهی TSMC اعلام کرد، این شرکت تایوانی قرار است سراغ استفاده از مواد اولیهی جدیدی برای ساخت ویفر پردازشی برود.

به گفتهی مارک لیو، تمامی بخشهای صنعت تراشه باید در همکاری نزدیک باشند تا بتوان هر دو سال تراشههایی ساخت که دو برابر پرقدرتتر از نسل قبل هستند. لیتوگرافی پنج نانومتری TSMC که اکنون در تولید انبوه قرار دارد از این قاعده پیروی میکند و لیتوگرافی سه نانومتری نیز در تلاش برای حفظ این روند خواهد بود.