اینتل پردازندههای هوش مصنوعی نروانا را روی درگاه M.2 نصب میکند

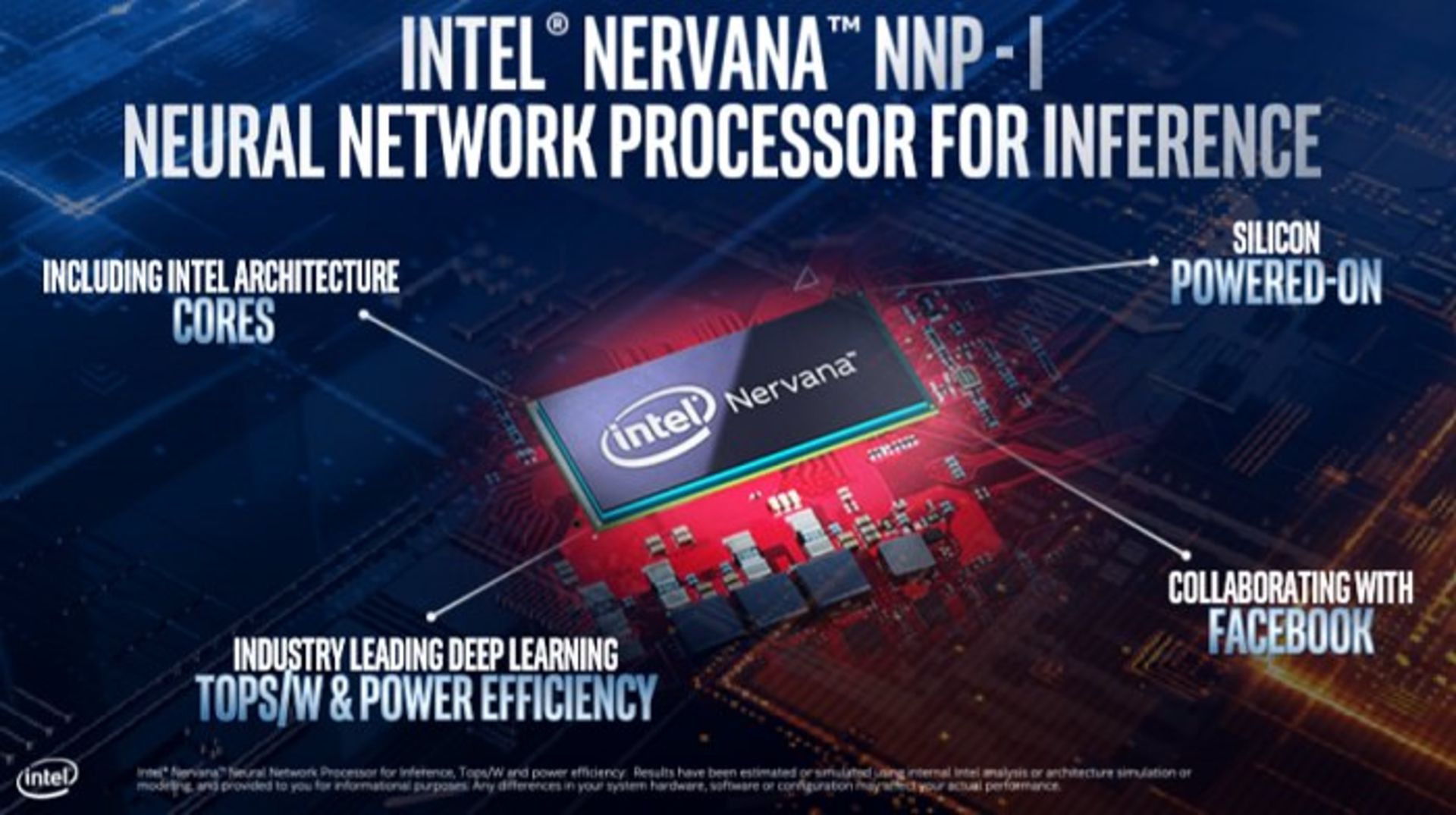

اینتل (Intel) چندی پیش اعلام کرد پردازندهی شبکهی عصبی استنتاجی نیروانا (Nervana Neural Network Processor for Inference)، یا به اختصار NNP-I، مانند یک پردازندهی ۱۰ نانومتری آیس لیک (Ice Lake) طراحی میشود که روی یک بورد به درگاه M.2 متصل خواهد شد. بله؛ درست خواندید؛ روی یک درگاه M.2 نصب خواهد شد؛ این نوع از درگاهها معمولا برای ذخیرهسازی استفاده میشوند. همچنین، اینتل برای ایجاد فضای کافی برای شتابدهندههای هوش مصنوعی، مواردی مانند هستههای گرافیکی و بلوکهای نمایشگر را که بخشهای مهمی از پردازندهی آیس لیک هستند، حذف کرده است.

اکنون دیگر دنیای هوش مصنوعی بهطور کامل در برابر چشمان انسانها قدبرافراشته و کمکم خیز برمیدارد تا تحولاتی بنیادین در محاسبات گوشیهای همراه، لپتاپها و کامپیوترهای رومیزی ایجاد کند؛ اما هنوز هم بیشتر حجم کاری هوش مصنوعی در مراکز دادهای اتفاق میافتد. کارهای آموزشی که نیاز زیادی به محاسبات دارد، شبکههای عصبی پیچیدهای ایجاد میکنند که عملیاتهای تشخیص شیء، ترجمهی گفتار، تلفیق صدا و کارهایی از این قبیل را انجام میدهد، اما این شبکهها نقطهی نهایی برای تکمیل و کار نیست. اصل مهم در استفاده از توانمندی هوش مصنوعی در مقیاس بزرگ مربوطبه استقرار مدلهای تکمیلشدهای است که ازطریق مرتبسازی و تجزیهوتحلیل روزانهی دادههای جهان، آنها را بررسی میکند. این همان کاری است که استنتاج نامیده میشود.

حجم کاری فرایندهای استنتاجی بسیار سبکتر از حجم کاری فرایندهای آموزشی است؛ بنابراین ایجاد مدل برای آنها مستلزم استفاده از پردازندهها و FPGAهای قدرتمند نیست. اما این کار هم مانند هر نوع کار محاسباتی دیگر در انتها به یک موضوع ختم میشود: هزینه. به عبارت دیگر، پیشهزینهی ارزان برمبنای «عملکرد در ازای وات» برای استنتاج از اهمیت بیشتری برخوردار است و به همین دلیل است که اینتل به این فکر میکند که شتابدهندههای NNP-I خود را در یک درگاه M.2 جای بدهد. این کار برای کاستن از حجم کاری ناشی از استنتاجهای زیاد در سرورهای Xeon انجام میشود و تراشهی بزرگتر را برای کارهای محاسباتی عمومی آزاد میکنند.

نصب شتابدهندهی NNP-I در درگاههای M.2 به کاهش بار کاری ناشی از استنتاج در سرورهای Xeon میانجامد

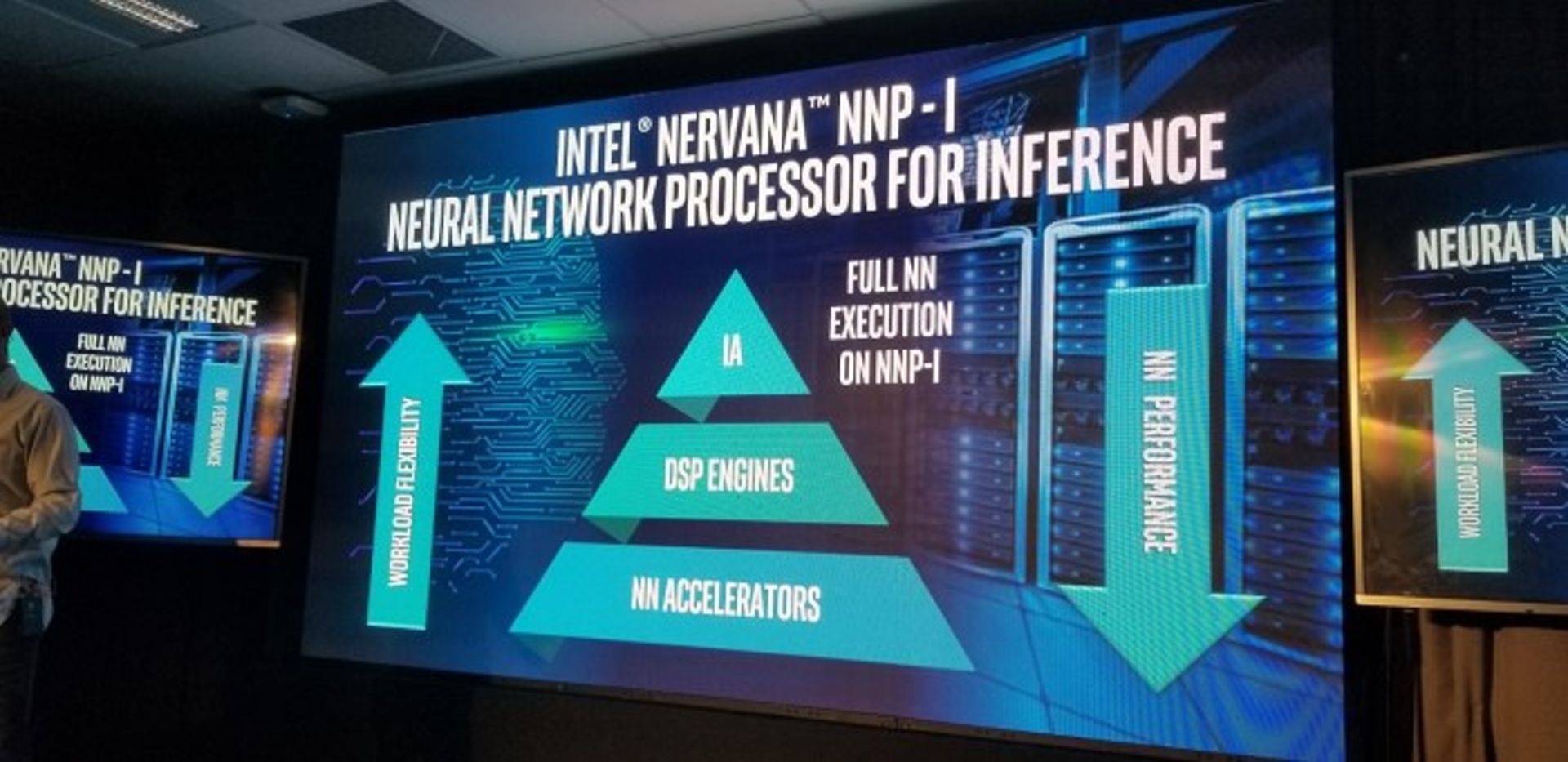

اینتل بلوک پردازنده در طراحی اصلی آیس لیک (که در تصویر بالا نشان داده شده است) را طوری دستکاری کرد تا برای حجم کاری هوش مصنوعی مناسب باشد. پکیج استاندارد آیس لیک به همراه پردازنده و هاب کنترلر پلتفرم (PCH) در این قطعه روی یک بورد واحد قرار گرفتهاند؛ اما اینتل بلوکهای نمایشگر و GPU را از روی این سطح برداشته و جای آنها را به موتور سفارشیسازیشدهی هوش مصنوعی داده است که کاربرد آنها منحصر به انواع خاصی از کدهای استنتاجی است. علاوه بر این، اینتل موتورهای DSP را هم به آنها اضافه کرده است. این موتورها برای الگوریتمهایی استفاده میشوند که مخصوص بلوکهای شتابدهنده با عملکرد ثابت نیست و به سازگاری مدنظر برای فضای هوش مصنوعی سریعالعمل کمک میکند.

اینتل جزئیات بیشتری از بلوکهای شتابدهنده فاش نکرده است؛ اما به احتمال زیاد آنها از مجموعهای از عناصر تکراری استفاده میکنند که شباهت زیادی به یک پردازندهی گرافیکی دارد. با وجود زیرسیستم قدرتمند حافظهی Gen11 که هماکنون در این فناوری قدرتمند استفاده میشود، به احتمال زیاد شرکت تصمیم خواهد گرفت که جای واحدهای اجرای گرافیک (EU) را با منطق سفارشی عوض کند (یا شاید واحدهای موجود را اصلاح کند). این در حالی است که باید ساختارهای تکمیلی و اتصالی بین واحدها را به همان صورت حفظ کند.

پردازنده در این طراحی همچنان دارای چندین هستهی محاسباتی معماری اینتل x86 هستند. البته، اینتل تعداد هستههایی که از میکرو معماری Sunny Cove استفاده میکنند، را فاش نکرده است. اورین گرشان (Oren Gershon)، مدیر کل بخش مهندس محصولات استنتاجی در اینتل، توضیح واضحی نمیدهد و تنها میگوید چندتا از هستهها را حذف کردهاند تا فضای خالی کافی برای قطعات دیگر فراهم شود. بنابراین شاید این پردازندههای آیس لیک چهار هستهای از حالا به بعد فقط دو هستهای باشند.

اینتل این پکیج را روی انواع مختلفی از کارتهای توسعه نصب میکند؛ مثلا نوع M.2 که بالا نشان داده شد، این قابلیت را دارد که به درگاه استاندارد M.2 در یک مادربورد سرور متصل شود. حتی میتوان آن را به کارتهای توسعهای بزرگتر روی اسلات PCIe هم متصل کرد. برخلاف برخی از سیلیکونهای سفارشی مانند TPU گوگل که برای هوش مصنوعی طراحی شدهاند، این دستگاه از نظر سختافزاری تقریبا با همهی سرورهای مدرن موجود سازگاری کامل دارد. این رویکرد کاملا مقیاسپذیر است: میتوان هرچند NNP-I که لازم باشد را به سرور اضافه کرد، بهویژه با استفاده از کارتهای رایزری که در درگاههای M.2 قرار میگیرند.

اینتل میگوید NNP-I از نظر توان طراحی حرارتی (TDP) برابر با پردازندههای آیس لیک است؛ یعنی حداکثر TDP درنظر گرفتهشده برای آنها درحدود ۲۸ وات است؛ اما باید توجه داشت که محدودیت ۱۵ واتی در رابطهای M.2 مانع از انتقال قدرت به دستگاههای کوچکتر میشود. اگر NNP-I به کارتهای توسعه وصل شوند خواهند توانست با حداکثر TDP فعالیت کنند؛ یعنی عملکرد خیلی بهتری خواهند داشت.

NNP-I از نظر توان طراحی حرارتی (TDP) با پردازندههای آیس لیک برابر هستند

اینتل برای انتقال کامل وظایف استنتاجی به شتابدهنده از نرمافزار مخصوصی استفاده خواهد کرد تا پردازندهی Xeon را از تکمیل کار آگاه کند. این انتقال باعث حذف ارتباطات رفتوبرگشتی در گذرگاه PCIe با شتابدهندههای دیگر میشود. این کار بار اضافی به پردازنده تحمیل میکند؛ چرا که ایجاد وقفه میکند و دادهها را به حرکت وامیدارد. در مقابل، NNP-I بهعنوان یک سیستم مستقل با سازوکار ورودی / خروجی خود (PCH) عمل میکند که امکان دسترسی به دادههای موردنیاز برای پردازش را فراهم میکند. عملیاتهای مربوطبه هوش مصنوعی دادهها را با ولع تمام میبلعند و همین عامل موجب میشود که اتصال ۳ در ۴ و نسبتا باریک PCIe بهصورت تنگنایی در پهنای باند به نظر برسد. اما، اینتل به کاربرانش اطمینان میدهد که فشار کاری تحلیلی ویدیویی با دادههای زیاد را تست کرده و هیچ محدودیتی در آن ندیده است. بلکه برعکس؛ اینتل معتقد است این نوع از حجمهای کاری در واقع از نظر محاسباتی محدود هستند.

هستههای x86 از دستورالعمل یادگیری عمیق VNNI اینتل (که به نام DL Boost هم شناخته میشود) پشتیبانی میکند. این دستورالعمل از AVX-512 برای ارتقای عملکرد استفاده میکند. اینتل ادعا میکند انعطافپذیری بالای حاصل از این کار تقریبا مناسب هر نوع از حجم کاری هوش مصنوعی است؛ بهویژه مواردی که از تناسب کافی برای موتورهای هوش مصنوعی یا DSP برخوردار نیستند. علاوهبراین، اینتل کامپایلری ارائه کرده است که کد را با شتابدهندههای NNP-I سازگار میکند. فیسبوک، در طور توسعهی این فناوری، «شریک تعریفی» اینتل برای حصول اطمینان از پشتیبانی کامپایلر Glo از این قطعهی سختافزاری بود. از این گذشته، این دستگاه از همهی زبانهای استاندارد مانند PyTorch و TensorFlow هم، با کمترین تغییرات، پشتیبانی میکند.

موضوع بسیار مهمتری که گرشون به آن اشاره میکند آن است که کارایی NNP-I بسیار شگفتانگیز و بسیار بهتر از CPU یا GPUهایی است که دستورهای چندگانهای دارند. برنامهها در مراکز دادهای، اپلیکیشنهای استنتاجی از رواج بیشتری نسبت به اپلیکیشنهای آموزشی برخوردار هستند و این دستگاههای کارآمد، توان مقرونبهصرفهای را بهصورت یکجا و یکدفعه به سرویسدهندگان کلاد (CSP) و هایپراسکالرها ارائه میدهند؛ به عبارت دیگر این بخش میتواند بخشی سودآور برای اینتل باشد. اینتل قصد ندارد این دستگاهها را بهتنهایی و بهصورت خردهفروشی به بازار عرضه کند، بلکه میخواهد کاری کند که CSPها در آینده ازطریق نمونههای مبتنی بر کلاد با این فناوری آشنا شوند.

اینتل هنوز هیچ اطلاعات عملکردی در پشتیبانی از ادعای جسورانهی خود در زمینهی کارایی حاصل از این محصول رو نکرده است؛ بلکه تنها نمونههایی از آن را در اختیار چند مشتری قرار داده است و پیشبینی میکند که تولید انبوه آن در ادامهی سال جاری آغاز خواهد شد. انتظار میرود انویدیا، تولیدکنندهی GPUهای Tesla T4 برای عملیاتهای استنتاجی، و کوالکام، توسعهدهندهی پردازندههای Cloud AI 100 مبتنی بر M.2، این ادعاها و اخبار را به دقت دنبال کنند.

نظرات