اینتل معماری جدیدی برای پردازنده های زئون و اسکایلیک-ایکس معرفی کرد

آکیلیش کومار، معمار پردازندههای سری اسکایلیک-اسپی اینتل، امروز در پستی که در وبلاگ شخصیاش منتشر کرد از معماری مش (Mesh) جدید اینتل برای پردازندههای با بستر مقیاسپذیر سری زئون خبر داد.

پردازندههای با بستر مقیاسپذیر اینتل، در واقع تغییر نام تجاری خط تولید پردازندههای محبوب سری زئون است و با توجه به استفادهی مکرر اینتل از دای پردازندههای بهینهشده برای سرور، در خط تولید پردازندههای سرور و کامپیوترهای رومیزی سطح بالا، این معماری جدید توانسته است راه خود را به سری جدید پردازندهی اسکایلیک-ایکس باز کند.

توپولوژی شبکهای جدید اینتل برای رقابت با تکنولوژی اینفینیتی فبریک شرکت AMD معرفی شده است. تکنولوژی اینفینیتی فبریک در پردازندههای سری رایزن، ترد ریپر و اپیک شرکت AMD وجود دارد. در ادامه به مقایسهی این دو طراحی میپردازیم.

دورهی باسهای حلقهای اینتل

کار اصلی پردازنده، پردازش داده است که برای این کار به جریان داده بین عناصر اصلی پردازنده نیاز است. بیتهایی که نمایندهی صفر و یک هستند، توسط سیمهایی در ابعاد نانو، با سرعت میلیاردها سیکل ساعت بر ثانیه داخل پردازنده جابجا میشوند. انتقال داده بین عناصر اصلی یک پردازنده مانند هسته، حافظه و کنترلکنندههای ورودی و خروجی، یکی از سختترین چالشهای پیش روی طراحان پردازنده است.

انتقال داده بهصورت کارآمد تأثیر بسیار زیاد و مستقیمی بر کارایی دارد و از آنجایی که انتقال داده به توان احتیاج دارد، در مصرف توان نیز بسیار تأثیرگذار است. کاهش مصرف توان هم باعث تولید گرمای کمتر توسط پردازنده میشود. در عوض اتلاف انرژی، اتصالهای بهینهشده به معمارهای کامپیوتر اجازه میدهد این توان را در بخشهای مهمتری مانند پردازش داده مصرف کنند. در سالهای گذشته تکنیکهای زیادی برای انتقال داده بین هستههای پردازندهها استفاده شده؛ ولی معماری حلقهای اینتل در نسلهای گذشتهی پردازندههای این شرکت استفاده شده است.

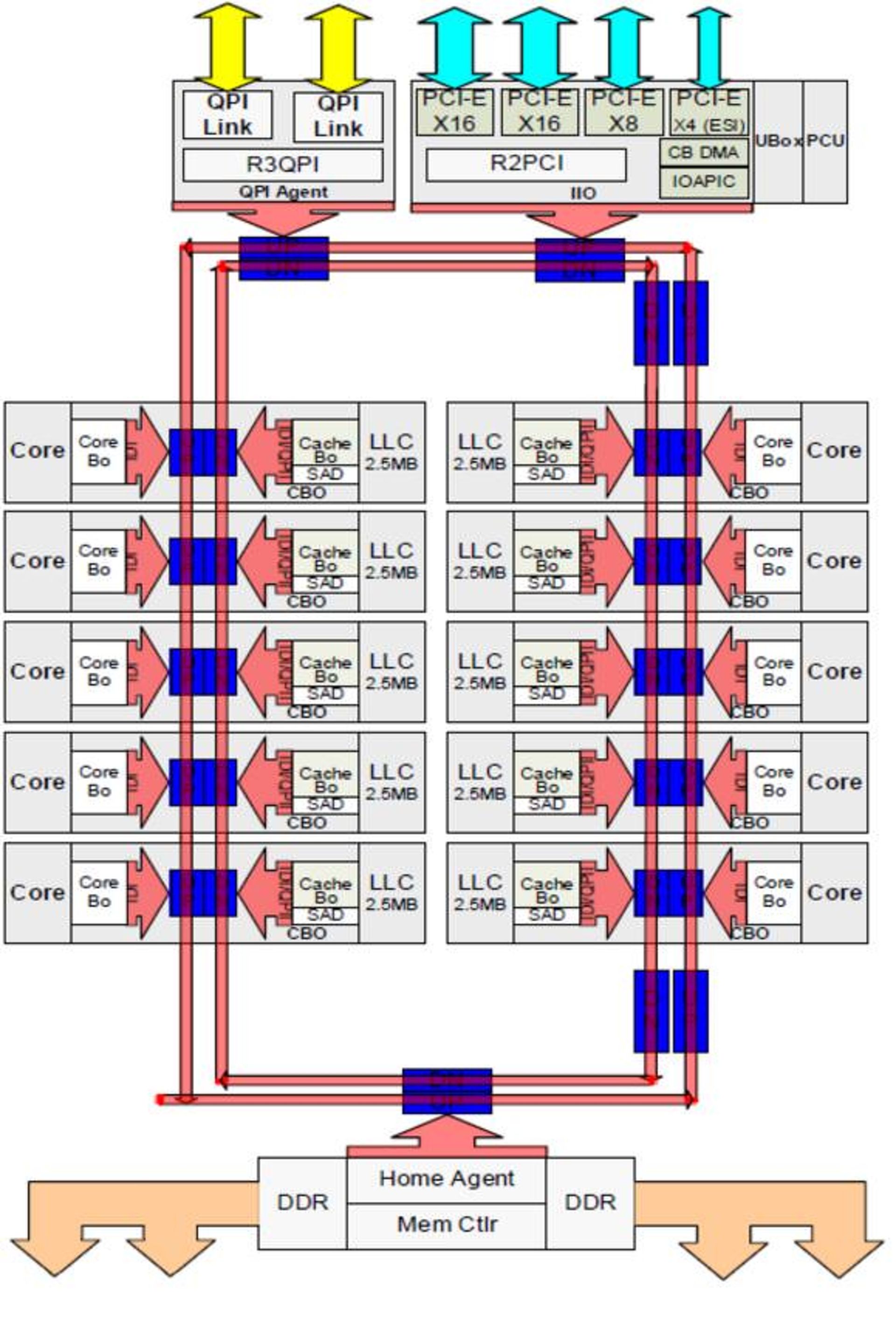

باس حلقهای اینتل که در شکل بالا در یک دای سری برادول از نوع کم هسته یا بهطور مختصر (LLC) نشان داده شده، اجزا مختلف پردازنده را با یک باس دوطرفه - که با رنگ قرمز نشان داده شده است - به یکدیگر متصل میکند. دای از نوع LLC از یک باس تک حلقه بهره میبرد که دادهها را با سرعت یک سیکل ساعت بین دو هسته مجاور جابجا میکند. طبیعتا جابجایی داده به هستههای دورتر تعداد سیکل بیشتری مصرف میکند و در نتیجه تأخیر انتقال نیز بیشتر میشود. برای مثال انتقال داده به دورترین هسته، ۱۲ سیکل ساعت طول میکشد. از آنجایی که باس دوطرفه است، مسیریابی داده برای پیدا کردن کوتاهترین مسیر بین دو هسته را میسر میکند.

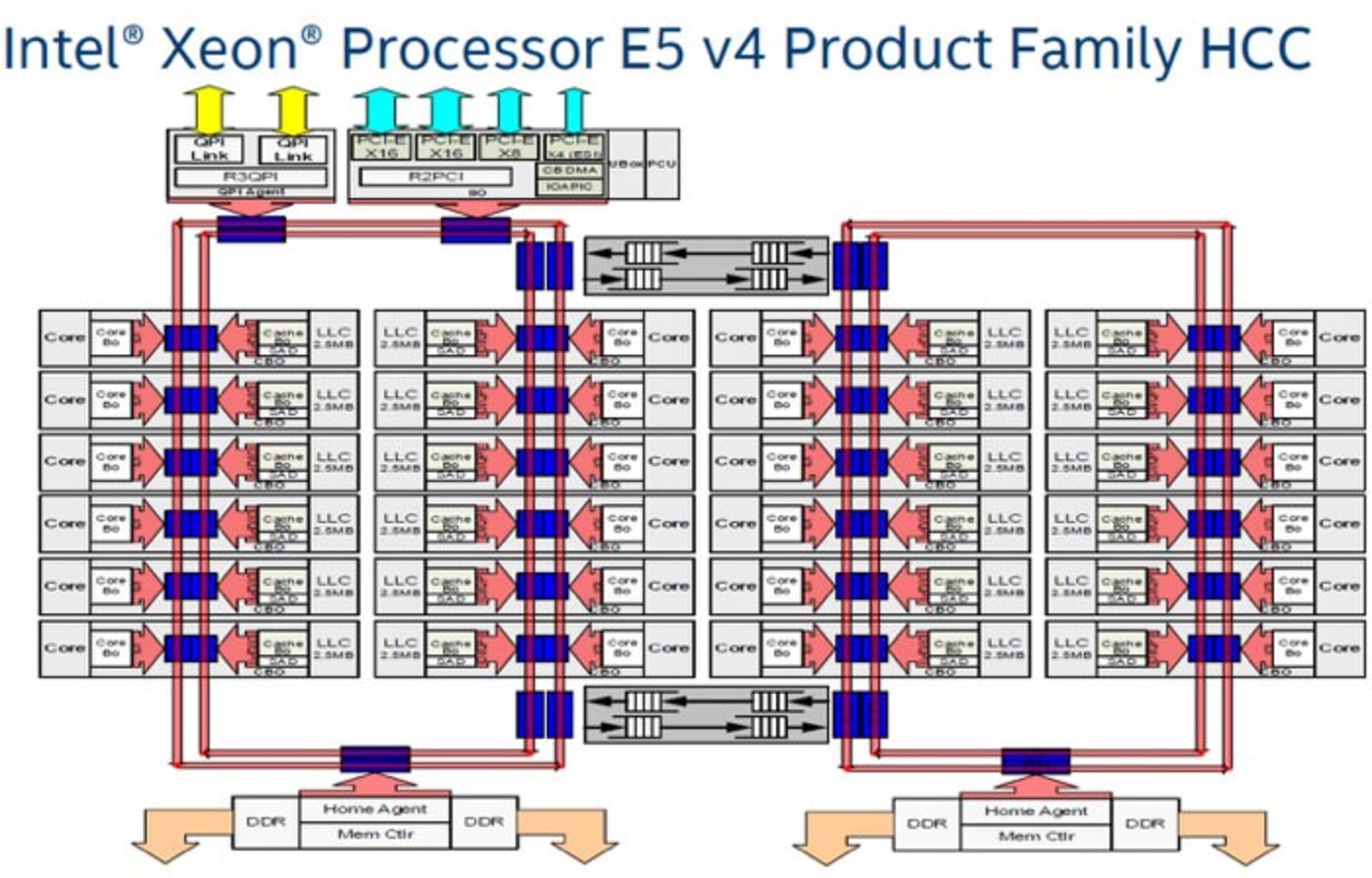

معماریهای با تعداد هستههای بالا یا بهاختصار (HCC) اشکالات این رویکرد را مشخص میکنند. برای افزایش تعداد هستهها و کشها، دایهای HCC از باس حلقهای دوتایی بهره میبرند. ارتباط بین دو حلقه از طریق یک سوییچ بافردار برقرار میشود (در شکل بین دو حلقه در بالا و پایین). عبور از سوییچ هزینهای برابر با ۵ سیکل ساعت دارد؛ که با توجه به تأخیر جابجایی اطلاعات در داخل هر حلقه، عملا این معماری امکان مقیاسپذیری بالایی ندارد. تأخیر ارتباط بین هستهها با بیشتر شدن تعداد هستهها افزایش مییابد و کاهش کارایی را به دنبال دارد. برای جبران کاهش کارایی میتوان فرکانس را افزایش داد که افزایش فرکانس هم باعث افزایش توان مصرفی و تولید حرارت بیشتر میشود.

معماری مش

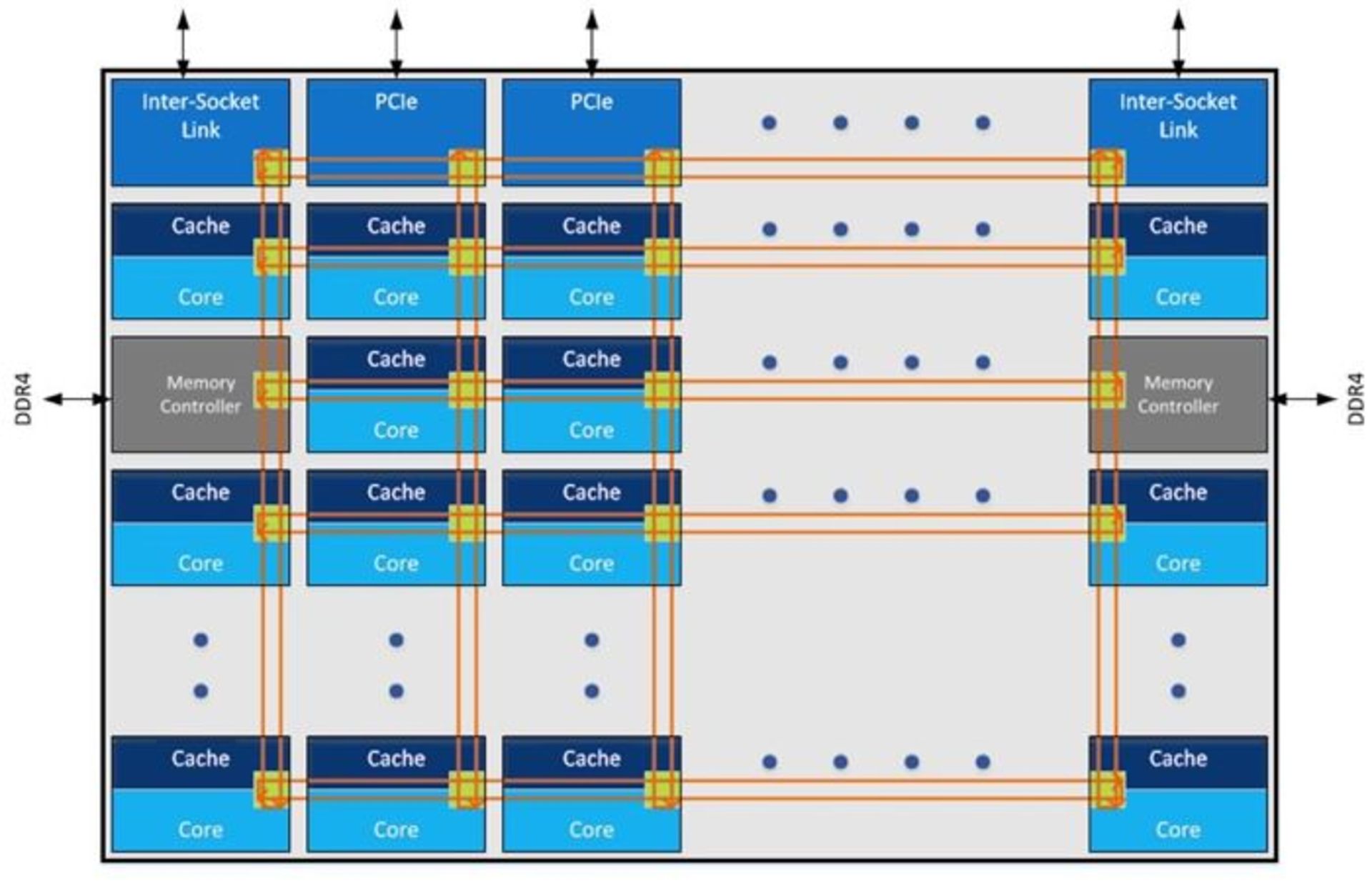

اینتل معماری مش را برای اولین با در سری پردازندههای نایتز لندینگ معرفی کرد، ولی استفاده از این معماری برای پردازندههای سرور و کامپیوترهای رومیزی سطح بالا، سطح جدیدی از بهرهوری اتصالات و در نتیجه افزایش کارایی را به همراه خواهد داشت. علاوه بر اتصالات، ویژگی جدید این معماری جابجایی کنترلرهای DDR4 به سمت راست و چپ دای است؛ بر خلاف معماریهای حلقهای که در قسمت پایین قرار داشت.

اینتل در توپولوژی مش جدید، هسته، کش، حافظه و کنترلرهای ورودی و خروجی را در ردیفهای افقی و عمودی به یکدیگر متصل کرده است. نکتهی قابل توجه عدم وجود سوییچهای بافردار (که یکی از عوامل کندکنندهی اتصالات بود) است. وجود سوییچهای واقع در تقاطع اتصالات، امکان ارتباط مستقیم و زمانبندی هوشمند برای پیدا کردن کوتاهترین مسیر بین اجزا را فراهم کرده است. همچنین یک طراحی حلقه مانند در اتصالات وجود دارد که امکان ایجاد زمانبندی بهینه در مسیر داده را فراهم میکند.

قابلیت جابجایی داده بهصورت پلهای بین هستهها، امکان مسیریابی پیچیدهتر ولی مؤثر بین عناصر دای را امکانپذیر میکند. طبق گزارش اینتل، معماری حلقهی جدید پهنای باند را هم افزایش داده است که در نتیجه سرعت انتقال داده بین هستهها و کشهایی که آنها را تغذیه میکنند، افزایش پیدا کرده است. معماری مش ترافیک دادهی ورودی و خروجی حافظهی اصلی را هم کنترل میکند و باعث افزایش بازدهی و کاهش تأخیر رم نیز شده است.

در قسمت بالای دای، جریان داده از کنترلرهای PCI در کنار دو کانال ارتباطی بین سوکت برقرار است. کانالهای ارتباطی بین سوکت، جریان داده بین تعداد پردازندههای بیشتر از دو عدد را برای تنظیمات مخصوص شبکه مدیریت میکنند. در گذشته اینتل از تکنولوژی (QPI) برای ارتباط بین سوکتها استفاده میکرد؛ ولی شایعات خبر از استفاده از کانال ارتباطی جدید در سری پردازندهی جدید اسکایلیک در مدل سرور میدهند. اینتل بهطور دقیق فرکانس کاری معماری مش جدید را اعلام نکرده است،؛ ولی طبق گزارش اینتل، فرکانس و ولتاژ کاری پایینتری نسبت به معماری حلقه دارد و در عین حال پهنای باند و تأخیر کمی هم دارد.

از سری اسکایلیک-ایکس چه میدانیم؟

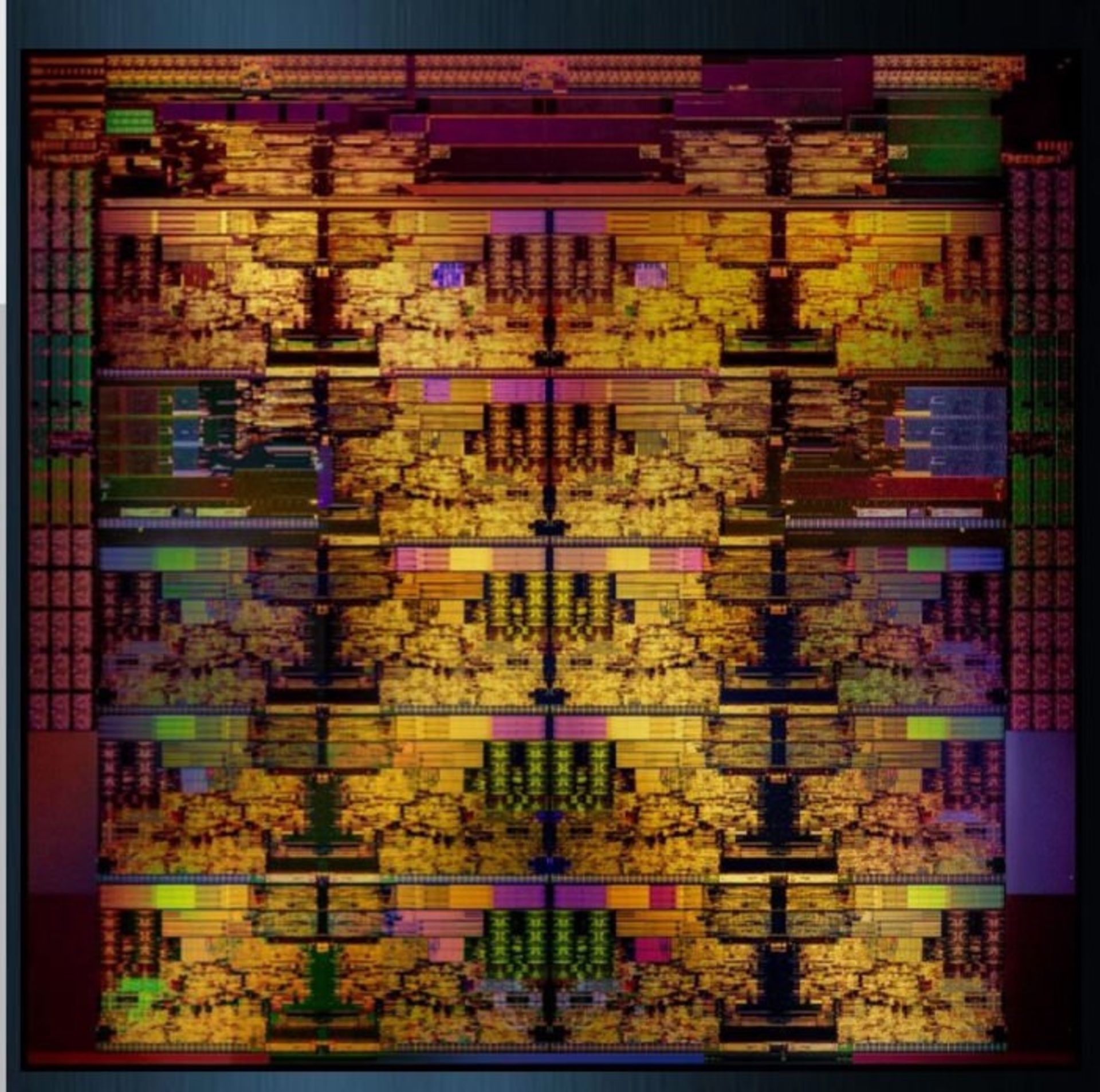

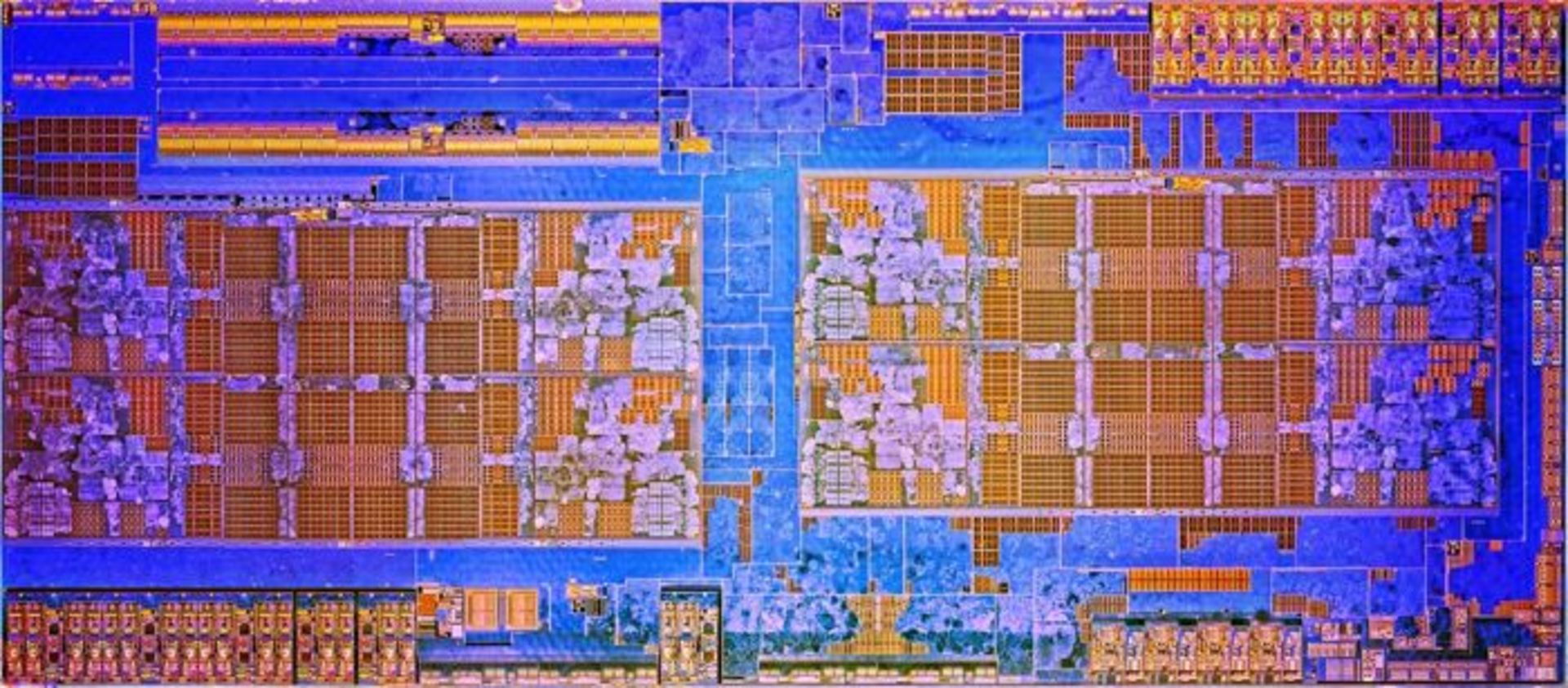

اینتل تصویری از دای معماری HCC خود که در سری اسکایلیک-ایکس استفاده شده، منتشر کرده است. اینتل در سری زئون نیز از معماری مش مشابهی استفاده کرده بود.

در تصویر بالا، بهراحتی میتوان کنترلرهای DDR4 را در سمت راست و چپ دای (ردیف دوم سمت چپ و راست) مشاهده کرد. اما درحالیکه به نظر میرسد این دای شامل ۲۰ هسته است، تنها ۱۸ هسته دارد. این تعداد هسته تا اینجا بیشترین تعداد هستهی موجود در سری اسکایلیک-ایکس بوده است.

نمودار مش اینتل مشخص میکند که اتصالات درون مش در سمت راست هر هسته قرار دارد ولی طبق تصویر دای، این اتصالات در تمام هستهها در سمت راست قرار ندارد. برای مثال در سمت چپترین ستون، اتصالات درون مش در محدودهی بالا سمت راست هسته واقع شده است؛ ولی در سمت راستترین ستون، این اتصالات در جهت قرینه یعنی بالا سمت چپ قرار دارند. این روش چینش اتصالات در فاصلهی بین هستهها تأثیر مستقیم دارد و در نتیجه برای انتقال داده بهصورت افقی به تعداد سیکلهای بیشتری نیاز است. برای مثال برای انتقال داده بهصورت عمودی، به ازای هر سطر به یک سیکل نیاز است؛ ولی برای انتقال داده بهصورت افقی از ستون دو به سه، به تعداد سیکل بیشتری نیاز است. باید در آینده منتظر انتشار جزئیات بیشتری از سوی اینتل باشیم.

در هر صورت، معماری مش امکان مقیاسپذیری بینظیری نسبت به معماری قبلی فراهم کرده است و با توجه به اینکه اینتل از معماری حلقهای در چندین نسل از پردازندههایش استفاده کرد، انتظار میرود در سالهای آینده از معماری مش در پردازندههای این شرکت استفاده شود. این معماری به اینتل امکان افزایش تعداد هستهی پردازندههایش، بدون افزایش تأخیر و توان مصرفی را میدهد.

از AMD چه خبر؟

صحبت از معماریهای اینتل بدون مقایسه با آخرین معماری AMD ناقص است. AMD هم یک اتصال جدید از نوع اینفینیتی فبریک طراحی کرده که ورژن بهینهشدهی هایپر ترانسپرت است که در میکرومعماری ذن به کار میرفت. خوشبختانه اطلاعات بیشتری درباره اتصالات برون هستهای AMD در اختیار داریم.

AMD در سری پردازندههای ذن، روش متفاوتی برای طراحی پردازنده انتخاب کرده است. میکرومعماری ذن از بلوکهای ۴ هستهای که CPU Complex یا بهاختصار CCX نامیده میشوند، بهره میبرد. AMD هر بلوک را با استفاده از کشهای ۸ مگابایتی به ۴ بخش تقسیم میکند؛ هر هسته با میانگین تأخیر مشابه به این کشهای L3 دسترسی دارد. با استفاده از ۲ بلوک CCX یک پردازندهی ۸ هستهای رایزن 7 ساخته میشود (بلوکهای نارنجی در تصویر بالا). این بلوکها توسط یک اتصال از نوع اینفینیتی فبریک به یکدیگر متصل میشوند. CCX-ها کنترلر حافظهی مشترکی دارند. پردازنده اصلی که در واقع دو پردازندهی ۴ هستهای است، توسط یک مسیر اینفینیتی فبریک با یکدیگر ارتباط برقرار میکنند. اینفینیتی فبریک، یک مسیر ارتباطی ۲۵۶ بیتی دوطرفه است که وظیفهی جابجایی ترافیک بین بلوکها را بر عهده دارد.

هرچند تأخیر ارتباط هستهها با یکدیگر در یک CCX به دلیل استفاده از حافظه مشترک یکسان است؛ واکشی داده از سایر بلوکها با تأخیر عبور از اینفینیتی فبریک همراه است. ارتباط بین تِرِدهایی که در بلوکهای مختلف قرار دارند هم از این تأخیر رنج میبرد. معماری AMD برتری زیادی نسبت به معماری حلقهی اینتل داشت؛ زیرا AMD بهراحتی میتوانست با افزایش تعداد بلوکها در یک تراشه، تعداد هستهها را افزایش بدهد. انتظار میرود پس از معرفی معماری مش اینتل، پردازندههای این شرکت نسبت به پردازندههای AMD برتری پیدا کنند؛ ولی این نکته را هم باید در نظر گرفت که بهینهسازیهای نرمافزاری میتواند بسیاری از مشکلات تأخیر اینفینیتی فبریک را رفع کنند.

با اندازهگیری تأخیر اینفینیتی فبریک در پردازنده مدل AMD Ryzen 5 1600X، متوجه میشویم که تأخیر اینفینیتی فبریک به فرکانس مموری وابسته است. از طرفی در تأخیر معماری حلقهای اینتل با افزایش فرکانس مموری کاهش خاصی در تأخیر مشاهده نشد. باید تا تست پردازندههای سری اسکایلیک صبر کنیم تا تأثیر فرکانس مموری بر تأخیر این معماری جدید را بسنجیم.

رقابت همچنان ادامه دارد

با معرفی معماریهای جدید هر دو شرکت که هر دو نسبت به نسلهای قبل از خود پیشرفتهای چشمگیری دارند، رقابت همچنان برای نسلهای آینده ادامه دارد.

هر معماری نقاط قوت و نقاط ضعف مربوط به خود را دارد و بهترین راه برای مقایسه، مقایسهی آنها بعد از پیادهسازی روی سیلیکون است.

نظرات